硅芯片上直接堆疊第二層晶體管 三維晶體管陣列有望打破摩爾定律

來源:科技日報 時間:2019-11-21 11:07:27

目前,用于計算機處理器的硅集成電路正接近單個芯片上晶體管的最大可行密度,至少在二維陣列中是這樣。摩爾定律看似已難以維持。美國密歇根大學一研究團隊卻另辟蹊徑,將晶體管陣列帶入三維空間,在最先進的硅芯片上直接堆疊第二層晶體管。這一研究為開發(fā)打破摩爾定律的硅集成電路鋪平了道路。

摩爾定律認為,集成電路上可容納的晶體管數(shù)目,約每隔兩年便會增加一倍。目前硅集成電路的晶體管密度已接近極限。而隨著硅晶體管尺寸變得越來越小,它們的工作電壓也在不斷下降,導致最先進的處理芯片可能會與觸摸板、顯示驅動器等高電壓接口組件不兼容,后者需要在更高電壓下運行,以避免錯誤的觸摸信號或過低亮度設置之類的影響。這就需要額外的芯片來處理接口設備和處理器之間的信號轉換。

為解決上述問題,密歇根大學研究人員通過附加器件層的單片三維集成,來提高硅互補金屬氧化物半導體集成電路的性能。他們首先使用含鋅和錫的溶液覆蓋硅芯片,在其表面形成均勻涂層,隨后短暫烘烤使其干燥,經(jīng)過不斷重復后制成一層約75納米厚的氧化鋅錫膜。使用該氧化鋅錫膜制造的薄膜晶體管可以承受比下方硅芯片更高的電壓。

為了解決兩個器件層之間的電壓失配問題,研究人員采用了頂部肖特基、底部歐姆的接觸結構,在觸點添加的肖特基門控薄膜晶體管和垂直薄膜二極管具有優(yōu)良的開關性能。測試顯示,在集成了高壓薄膜晶體管后,基礎硅芯片仍然可以工作。

研究人員表示,硅集成電路在低電壓(約1伏)下工作,但可以通過單片集成薄膜晶體管來提供高電壓處理能力,從而免除了對額外芯片的需求。他們的新方法將氧化物電子學的優(yōu)勢引入到單個硅晶體管中,有助于更緊湊、具有更多功能的芯片的開發(fā)。

相關論文刊發(fā)在最新一期《自然·電子學》雜志上。

-

工信部:持續(xù)改善網(wǎng)絡基礎設施建設 引領帶動綠色智能家電消費 在自家冰箱上下單,就能收到北京寄來的地道烤鴨;只要進入千兆城市,就能享受遍布的極速WiFi……在國務院新聞辦公室日前舉行的例行吹風會...

工信部:持續(xù)改善網(wǎng)絡基礎設施建設 引領帶動綠色智能家電消費 在自家冰箱上下單,就能收到北京寄來的地道烤鴨;只要進入千兆城市,就能享受遍布的極速WiFi……在國務院新聞辦公室日前舉行的例行吹風會... -

打造低碳零碳負碳原創(chuàng)技術的策源地 中國環(huán)保發(fā)起雙碳科創(chuàng)園 5日,由中國環(huán)境保護集團(以下簡稱中國環(huán)保)發(fā)起的中國環(huán)保雙碳科創(chuàng)園暨中歐雙碳產(chǎn)業(yè)園(以下簡稱園區(qū))啟動會暨雙碳戰(zhàn)略座談會在北京市順義

打造低碳零碳負碳原創(chuàng)技術的策源地 中國環(huán)保發(fā)起雙碳科創(chuàng)園 5日,由中國環(huán)境保護集團(以下簡稱中國環(huán)保)發(fā)起的中國環(huán)保雙碳科創(chuàng)園暨中歐雙碳產(chǎn)業(yè)園(以下簡稱園區(qū))啟動會暨雙碳戰(zhàn)略座談會在北京市順義 -

支持資金近1.5億元!內蒙古啟動“雙碳”科技創(chuàng)新重大示范工程 記者6月7日從內蒙古科技廳獲悉,為將全區(qū)雙碳科技創(chuàng)新工作迅速落到實處,內蒙古按照圍繞產(chǎn)業(yè)鏈部署創(chuàng)新鏈、圍繞創(chuàng)新鏈布局產(chǎn)業(yè)鏈的原則,緊

支持資金近1.5億元!內蒙古啟動“雙碳”科技創(chuàng)新重大示范工程 記者6月7日從內蒙古科技廳獲悉,為將全區(qū)雙碳科技創(chuàng)新工作迅速落到實處,內蒙古按照圍繞產(chǎn)業(yè)鏈部署創(chuàng)新鏈、圍繞創(chuàng)新鏈布局產(chǎn)業(yè)鏈的原則,緊 -

我國首個!首批兩臺HXN6型內電混合動力機車成功下線 6月9日,我國首批兩臺商品化HXN6型內電混合動力機車在中車資陽機車有限公司(以下簡稱中車資陽公司)成功下線。該車動力源采用動力電池組+柴

我國首個!首批兩臺HXN6型內電混合動力機車成功下線 6月9日,我國首批兩臺商品化HXN6型內電混合動力機車在中車資陽機車有限公司(以下簡稱中車資陽公司)成功下線。該車動力源采用動力電池組+柴 -

好消息!2022年起企業(yè)可提前享受前三季度研發(fā)費用加計扣除政策 近日,國家稅務總局印發(fā)《關于企業(yè)預繳申報享受研發(fā)費用加計扣除優(yōu)惠政策有關事項的公告》,明確從2022年起,企業(yè)可以在每年10月申報期申報

好消息!2022年起企業(yè)可提前享受前三季度研發(fā)費用加計扣除政策 近日,國家稅務總局印發(fā)《關于企業(yè)預繳申報享受研發(fā)費用加計扣除優(yōu)惠政策有關事項的公告》,明確從2022年起,企業(yè)可以在每年10月申報期申報 -

智能中遇見“未來”!中新新天津生態(tài)城將推出6個智慧應用場景 第六屆世界智能大會云端召開在即。作為世界智能大會的永久展示基地,中新天津生態(tài)城今年將推出哪些值得期待的智慧應用場景?在智能中遇見未

智能中遇見“未來”!中新新天津生態(tài)城將推出6個智慧應用場景 第六屆世界智能大會云端召開在即。作為世界智能大會的永久展示基地,中新天津生態(tài)城今年將推出哪些值得期待的智慧應用場景?在智能中遇見未

-

【實探】中藥價格狂飆過后的“藥都”亳州:貨車司機閑坐等接單 【實探】中藥價格狂飆過后的“藥都”亳州:貨車司機閑坐等接單,當歸,黨

【實探】中藥價格狂飆過后的“藥都”亳州:貨車司機閑坐等接單 【實探】中藥價格狂飆過后的“藥都”亳州:貨車司機閑坐等接單,當歸,黨 -

東方日升(300118.SZ)擬10股派2元 于7月14日除權除息 智通財經(jīng)APP訊,東方日升(300118)(300118 SZ)公告,公司2022年年度權益

東方日升(300118.SZ)擬10股派2元 于7月14日除權除息 智通財經(jīng)APP訊,東方日升(300118)(300118 SZ)公告,公司2022年年度權益 -

中國蜀塔(08623)擬420萬元收購雅安寶盛金屬材料余下30%股權 智通財經(jīng)APP訊,中國蜀塔(08623)公布,于2023年7月7日,該公司全資附屬

中國蜀塔(08623)擬420萬元收購雅安寶盛金屬材料余下30%股權 智通財經(jīng)APP訊,中國蜀塔(08623)公布,于2023年7月7日,該公司全資附屬 -

南王科技最新公告:擬投建高端環(huán)保食品級紙制品項目 南王科技公告,公司擬在廣東省鶴山市鶴山工業(yè)城A區(qū)設立全資子公司“廣

南王科技最新公告:擬投建高端環(huán)保食品級紙制品項目 南王科技公告,公司擬在廣東省鶴山市鶴山工業(yè)城A區(qū)設立全資子公司“廣 -

南王科技(301355.SZ):擬設立子公司投資建設高端環(huán)保食品級紙制品項目 格隆匯7月7日丨南王科技(301355 SZ)公布,公司于2023年7月7日召開第三

南王科技(301355.SZ):擬設立子公司投資建設高端環(huán)保食品級紙制品項目 格隆匯7月7日丨南王科技(301355 SZ)公布,公司于2023年7月7日召開第三 -

拉夏貝爾(06116):管理人仍有序開展債權申報、債務及資產(chǎn)核查等工作 智通財經(jīng)APP訊,拉夏貝爾(603157)(06116)發(fā)布公告,自公司進入破產(chǎn)清算

拉夏貝爾(06116):管理人仍有序開展債權申報、債務及資產(chǎn)核查等工作 智通財經(jīng)APP訊,拉夏貝爾(603157)(06116)發(fā)布公告,自公司進入破產(chǎn)清算 -

2023年7月7日江蘇省聚丙烯酰胺價格最新行情預測 中國報告大廳2023年7月7日江蘇省聚丙烯酰胺價格最新走勢監(jiān)測顯示:蘇州

2023年7月7日江蘇省聚丙烯酰胺價格最新行情預測 中國報告大廳2023年7月7日江蘇省聚丙烯酰胺價格最新走勢監(jiān)測顯示:蘇州 -

CCER重啟真的要來了!生態(tài)環(huán)境部發(fā)布公開征求意見通知 CCER重啟真的要來了!生態(tài)環(huán)境部發(fā)布公開征求意見通知,配額,交易,ccer,

CCER重啟真的要來了!生態(tài)環(huán)境部發(fā)布公開征求意見通知 CCER重啟真的要來了!生態(tài)環(huán)境部發(fā)布公開征求意見通知,配額,交易,ccer, -

云南建投混凝土(01847)附屬高分子公司訂立保理協(xié)議 智通財經(jīng)APP訊,云南建投混凝土(01847)發(fā)布公告,于2023年7月7日,該公

云南建投混凝土(01847)附屬高分子公司訂立保理協(xié)議 智通財經(jīng)APP訊,云南建投混凝土(01847)發(fā)布公告,于2023年7月7日,該公 -

明源云(00909.HK)委任梁瑞冰為聯(lián)席公司秘書 格隆匯7月7日丨明源云(00909 HK)宣布,司徒嘉怡因其他工作安排,已提呈

明源云(00909.HK)委任梁瑞冰為聯(lián)席公司秘書 格隆匯7月7日丨明源云(00909 HK)宣布,司徒嘉怡因其他工作安排,已提呈 -

彩客新能源(01986)4月21日斥資8.58萬港元回購6.2萬股 智通財經(jīng)APP訊,彩客新能源(01986)發(fā)布公告,于2023年4月21日,該公司

彩客新能源(01986)4月21日斥資8.58萬港元回購6.2萬股 智通財經(jīng)APP訊,彩客新能源(01986)發(fā)布公告,于2023年4月21日,該公司 -

富祥藥業(yè):7月6日接受機構調研,包括知名機構盤京投資的多家機構參與 2023年7月7日富祥藥業(yè)(300497)發(fā)布公告稱公司于2023年7月6日接受機構

富祥藥業(yè):7月6日接受機構調研,包括知名機構盤京投資的多家機構參與 2023年7月7日富祥藥業(yè)(300497)發(fā)布公告稱公司于2023年7月6日接受機構 -

廣東宏大:預計2023年1-6月盈利,凈利潤同比增20%至30% 廣東宏大發(fā)布業(yè)績預告,預計2023年1-6月歸屬凈利潤盈利3 02億元至3 27

廣東宏大:預計2023年1-6月盈利,凈利潤同比增20%至30% 廣東宏大發(fā)布業(yè)績預告,預計2023年1-6月歸屬凈利潤盈利3 02億元至3 27 -

馮奎章_馮奎 1、馮奎賣妻是明朝末年的故事。2、《馮奎賣妻》保定府有一對夫妻叫馮奎

馮奎章_馮奎 1、馮奎賣妻是明朝末年的故事。2、《馮奎賣妻》保定府有一對夫妻叫馮奎 -

注意!家里這些物品也要“防暑降溫” 入夏以來,多輪高溫天氣來襲用電需求量較常年同期偏高面對“烤”驗日常

注意!家里這些物品也要“防暑降溫” 入夏以來,多輪高溫天氣來襲用電需求量較常年同期偏高面對“烤”驗日常 -

2023年愛心售報|小報童帶病堅持來賣報 孩子成長迅速讓家長很欣慰 揚子晚報7月7日訊(記者季宇軒實習生王元釗)7月6日是2023年揚子晚報暑

2023年愛心售報|小報童帶病堅持來賣報 孩子成長迅速讓家長很欣慰 揚子晚報7月7日訊(記者季宇軒實習生王元釗)7月6日是2023年揚子晚報暑 -

粵電力A最新公告:預計上半年凈利潤8億元-9.5億元 同比扭虧為盈 粵電力A公告預計上半年凈利潤8億元95億元去年同期虧損1372億元同比扭虧

粵電力A最新公告:預計上半年凈利潤8億元-9.5億元 同比扭虧為盈 粵電力A公告預計上半年凈利潤8億元95億元去年同期虧損1372億元同比扭虧 -

潼關黃金(00340.HK)擬3.39億港元收購宏勇投資100%股份 格隆匯7月7日丨潼關黃金(00340 HK)公告,于2023年7月7日,公司(作為買

潼關黃金(00340.HK)擬3.39億港元收購宏勇投資100%股份 格隆匯7月7日丨潼關黃金(00340 HK)公告,于2023年7月7日,公司(作為買 -

小摩:轉型和AI利好被負面因素抵消 首予IBM(IBM.US)“中性”評級 摩根大通分析師BrianEssex發(fā)表研報,首次覆蓋IBM(IBM US),給予“中性

小摩:轉型和AI利好被負面因素抵消 首予IBM(IBM.US)“中性”評級 摩根大通分析師BrianEssex發(fā)表研報,首次覆蓋IBM(IBM US),給予“中性 -

Wolfe下修派拉蒙環(huán)球(PARA.US)業(yè)績預期 降評級至“跑輸大盤” WolfeResearch將派拉蒙環(huán)球(PARA US)的評級從“與同行評級”下調為“跑

Wolfe下修派拉蒙環(huán)球(PARA.US)業(yè)績預期 降評級至“跑輸大盤” WolfeResearch將派拉蒙環(huán)球(PARA US)的評級從“與同行評級”下調為“跑 -

順豐控股最新公告:4月速運物流業(yè)務營業(yè)收入146.46億元 同比增長27.29% 順豐控股公告,4月速運物流業(yè)務營業(yè)收入146 46億元,同比增長27 29%;

順豐控股最新公告:4月速運物流業(yè)務營業(yè)收入146.46億元 同比增長27.29% 順豐控股公告,4月速運物流業(yè)務營業(yè)收入146 46億元,同比增長27 29%; -

青島銀行(03866.HK):提名陳霜及杜寧為董事候選人 格隆匯7月7日丨青島銀行(002948)(03866 HK)公布,董事會于2023年7月7日

青島銀行(03866.HK):提名陳霜及杜寧為董事候選人 格隆匯7月7日丨青島銀行(002948)(03866 HK)公布,董事會于2023年7月7日 -

深圳大動作!24條舉措 劍指… 作為全國外貿(mào)重鎮(zhèn),深圳在促進外貿(mào)穩(wěn)定健康發(fā)展上再加碼!日前,中國人

深圳大動作!24條舉措 劍指… 作為全國外貿(mào)重鎮(zhèn),深圳在促進外貿(mào)穩(wěn)定健康發(fā)展上再加碼!日前,中國人 -

我國人工智能蓬勃發(fā)展 核心產(chǎn)業(yè)規(guī)模達5000億元 7月6日,2023世界人工智能大會在上海世博中心拉開帷幕。圖為參觀者在達

我國人工智能蓬勃發(fā)展 核心產(chǎn)業(yè)規(guī)模達5000億元 7月6日,2023世界人工智能大會在上海世博中心拉開帷幕。圖為參觀者在達 -

李玟媽媽首度發(fā)聲,公開吐槽外國女婿缺點,李玟曾為老公整晚痛哭 閱讀此文前,誠邀您點擊一下“關注”,方便您隨時查閱一系列優(yōu)質文章,

李玟媽媽首度發(fā)聲,公開吐槽外國女婿缺點,李玟曾為老公整晚痛哭 閱讀此文前,誠邀您點擊一下“關注”,方便您隨時查閱一系列優(yōu)質文章, -

中國銀河(06881)因可轉債轉股2022年末期股息調整為每股0.22533元 智通財經(jīng)APP訊,中國銀河(601881)(06881)公布,由于公司于2022年3月24

中國銀河(06881)因可轉債轉股2022年末期股息調整為每股0.22533元 智通財經(jīng)APP訊,中國銀河(601881)(06881)公布,由于公司于2022年3月24 -

正業(yè)科技(300410.SZ)選舉余笑兵為董事長 智通財經(jīng)APP訊,正業(yè)科技(300410)(300410 SZ)公告,公司董事會同意選舉

正業(yè)科技(300410.SZ)選舉余笑兵為董事長 智通財經(jīng)APP訊,正業(yè)科技(300410)(300410 SZ)公告,公司董事會同意選舉 -

紫金礦業(yè)(02899.HK)預計上半年凈利約102億元 同比下降19.2% 格隆匯7月7日丨紫金礦業(yè)(02899 HK)公告,公司預計2023年半年度實現(xiàn)歸屬

紫金礦業(yè)(02899.HK)預計上半年凈利約102億元 同比下降19.2% 格隆匯7月7日丨紫金礦業(yè)(02899 HK)公告,公司預計2023年半年度實現(xiàn)歸屬 -

中航光電(002179.SZ):擬投資27.2億元在洛陽購置土地建高端互連科技產(chǎn)業(yè)社區(qū)項目 格隆匯7月7日丨中航光電(002179)(002179 SZ)公布,2023年7月7日,公司

中航光電(002179.SZ):擬投資27.2億元在洛陽購置土地建高端互連科技產(chǎn)業(yè)社區(qū)項目 格隆匯7月7日丨中航光電(002179)(002179 SZ)公布,2023年7月7日,公司 -

建發(fā)國際集團(01908.HK)根據(jù)以股代息計劃發(fā)行1.08億股 格隆匯7月7日丨建發(fā)國際集團(01908 HK)公布,根據(jù)公司以股代息計劃而于

建發(fā)國際集團(01908.HK)根據(jù)以股代息計劃發(fā)行1.08億股 格隆匯7月7日丨建發(fā)國際集團(01908 HK)公布,根據(jù)公司以股代息計劃而于

熱門資訊

-

源自福特超級平臺,江鈴福特新款輕客來襲 說起輕客,大家的第一印象總是全順...

源自福特超級平臺,江鈴福特新款輕客來襲 說起輕客,大家的第一印象總是全順... -

多彩新媒協(xié)同多省IPTV加速布局大屏生態(tài)圈,“看中國”深度挖掘 智能大屏價值 6月16日,在北京論道暨第25屆中國...

多彩新媒協(xié)同多省IPTV加速布局大屏生態(tài)圈,“看中國”深度挖掘 智能大屏價值 6月16日,在北京論道暨第25屆中國... -

出擊!招行信用卡協(xié)助警方重拳打擊金融“黑灰產(chǎn)”! 在上海浦東新區(qū)某大廈內,掛著“法...

出擊!招行信用卡協(xié)助警方重拳打擊金融“黑灰產(chǎn)”! 在上海浦東新區(qū)某大廈內,掛著“法... -

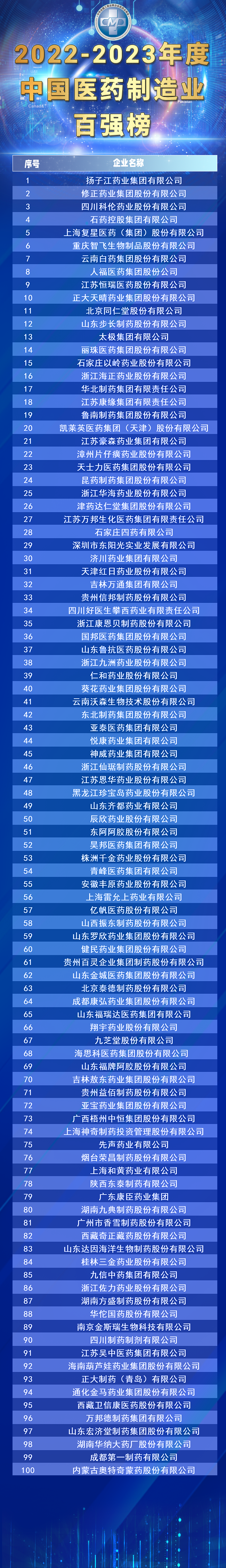

“2022-2023年度中國醫(yī)藥制造業(yè)百強”出爐,揚子江藥業(yè)集團榮登榜首 7月4日,由全國工商聯(lián)醫(yī)藥業(yè)商會、...

“2022-2023年度中國醫(yī)藥制造業(yè)百強”出爐,揚子江藥業(yè)集團榮登榜首 7月4日,由全國工商聯(lián)醫(yī)藥業(yè)商會、...

文章排行

圖片新聞

-

國慶假期懷柔北部山區(qū)的紅葉進入最佳觀賞期 吸引游客前來賞秋景 國慶假期,懷柔北部山區(qū)的紅葉進入...

國慶假期懷柔北部山區(qū)的紅葉進入最佳觀賞期 吸引游客前來賞秋景 國慶假期,懷柔北部山區(qū)的紅葉進入... -

重磅!四川省科創(chuàng)貸款較年初新增620.35億元 同比增長21.22% 記者日前從中國人民銀行成都分行獲...

重磅!四川省科創(chuàng)貸款較年初新增620.35億元 同比增長21.22% 記者日前從中國人民銀行成都分行獲... -

252項“全程網(wǎng)辦”!川渝兩地企業(yè)登記檔案實現(xiàn)跨區(qū)域互查 8月30日,記者從省大數(shù)據(jù)中心獲悉...

252項“全程網(wǎng)辦”!川渝兩地企業(yè)登記檔案實現(xiàn)跨區(qū)域互查 8月30日,記者從省大數(shù)據(jù)中心獲悉... -

2022年中國國際服務貿(mào)易交易會在京舉辦 四川參展企業(yè)數(shù)量創(chuàng)新高 8月31日至9月5日,主題為服務合作...

2022年中國國際服務貿(mào)易交易會在京舉辦 四川參展企業(yè)數(shù)量創(chuàng)新高 8月31日至9月5日,主題為服務合作...